従来、PIMアーキテクチャは「0」か「1」のデータしか扱えない2値(0, 1)SRAM構造のため、1ビット演算では大規模CNN演算に十分な演算精度を達成することができない。また、製造プロセスのばらつきも演算の信頼性を低下させる要因であり、対策が必要である。

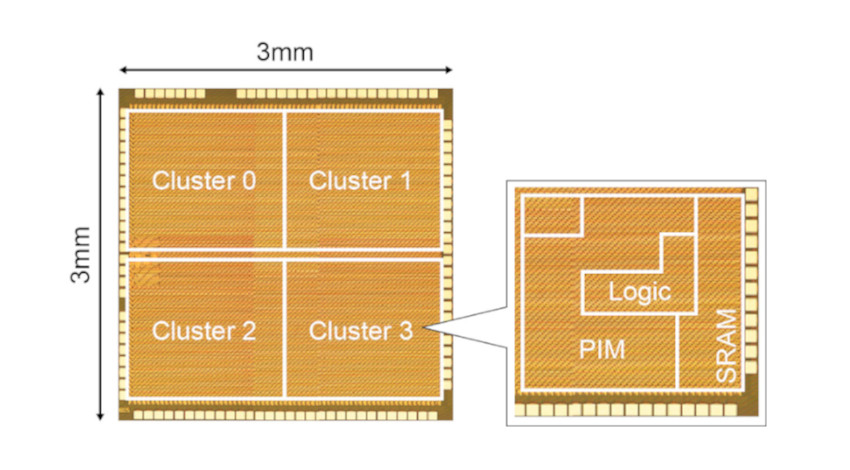

そこで、ルネサス エレクトロニクス株式会社は、低消費電力で高速にCNN(Convolutional Neural Network)処理を実現するAIアクセラレータを開発し、同アクセラレータを搭載したテストチップにて8.8 TOPS/W(※)の電力効率を実証した。

同アクセラレータは、メモリ回路内でメモリデータの読み出し中に積和演算まで行うProcessing-in-Memory(PIM)アーキテクチャをベースにしていまる。今回、同アクセラレータの実現のために、以下の技術も新たに開発した。これにより、ディープラーニング処理におけるメモリアクセス時間の短縮と、積和演算の消費電力低減を両立し、手書き文字認識(MNIST)で評価した結果、99%以上の認識率を保ちながら電力効率も達成することができた。

- 必要な演算精度に応じてビット数を調整する、3値(-1, 0, 1)SRAM構造のPIM

- コンパレータとレプリカセルを組み合わせたメモリデータ読み出し回路

- 製造プロセスのばらつきによる演算誤差抑制、ばらつき回避技術

今回新たに開発した3値(-1, 0, 1)SRAM構造のPIMアーキテクチャは、3値メモリと簡単なデジタル演算ブロックの組み合わせにより、ハードウェアの増加や演算誤差の増加を抑えつつ、必要精度に応じて演算ビット数を1.5ビット(3値)や4ビット演算などに切り替えが可能である。ユーザーごとに異なる演算規模と精度要求に対応可能なため、演算精度と消費電力のバランスを最適化できる。

PIMアーキテクチャを適用した場合、メモリデータはSRAM構造におけるビット線電流の値を検出することで読み出す。ビット線電流の検出にはアナログデジタル変換器(A/Dコンバータ)を用いるのが有効だが、この場合、高い消費電力とチップ面積の増大が課題となる。

今回、A/Dコンバータを用いず、コンパレータ(1ビットセンスアンプ)と電流値を自由に制御できるレプリカセルを組み合わせ、メモリデータ読出し回路を開発した。さらに、ニューラルネットワークの動作では活性化しているノード(ニューロン)は1%程度のごく一部であるという特性を活かし、非活性化ノードに対しては読み出し回路自体の動作を停止させることで、さらなる低電力化を実現した。

PIMは大幅な低電力化が可能な反面、製造プロセスのばらつきによる演算誤差が発生する課題がある。これは、製造プロセスのばらつきによって、SRAM構造におけるビット線電流の値に誤差が生じ、結果、メモリデータの読み出しに誤差が生じるからである。

そこで、チップ内に多数のSRAM演算回路ブロックを敷き詰め、製造プロセスのばらつきが小さいブロックで演算する方式を開発した。活性化しているノード(ニューロン)はごく一部である特性を利用し、製造プロセスばらつきの小さいSRAM演算回路ブロックに選択的に活性化ニューロンを配置し、演算する。これにより、演算誤差を低減できる。

※ Tera Operations per Second per Wattの略。1Wの電力で可能な演算回数を表す。8.8 TOPS/W は、1Wの電力で8.8兆回の演算が可能な性能。

無料メルマガ会員に登録しませんか?

IoTに関する様々な情報を取材し、皆様にお届けいたします。